I2C

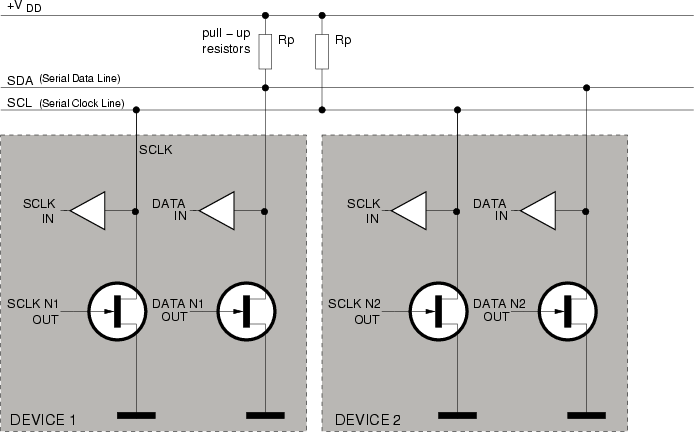

Der I²C-Bus basiert auf dem Master-Slave-Prinzip und besteht aus zwei Leitungen, einer Daten- und einer Taktleitung, die im Idle-Zustand durch Pullupwiderstände auf hohem Pegel gehalten werden. Der Takt wird stets vom Master generiert kann aber vom Slave solange auf 0 gehalten werden, bis der Slave wieder bereit ist. Die Daten können in beide Richtungen übertragen werden. Die Daten werden byteweise übertragen und jedes empfangene Byte wird durch einen Acknowledge-Impuls (0 = ACK / 1 = NAK) bestätigt. Die Treiber für den Takt und die Daten haben beim Master und beim Slave zum Beispiel den folgenden Aufbau.

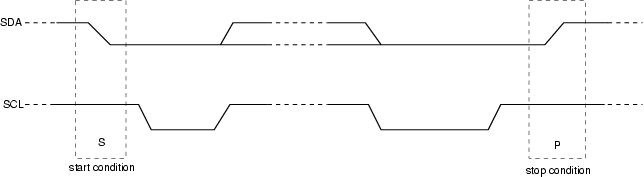

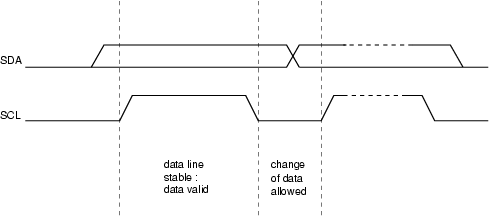

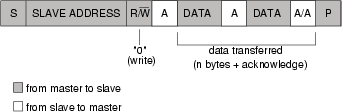

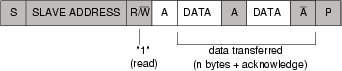

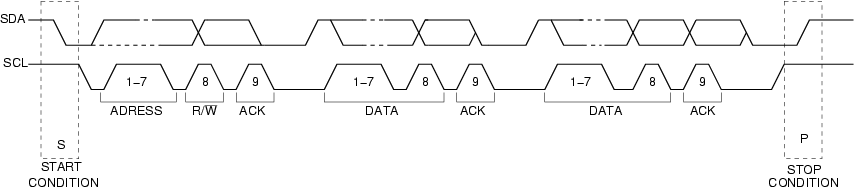

Will ein Master einen Transfer initiieren, überträgt er zunächst ein Startsymbol und dann eine Adresse. Der adressierte Slave bestätigt und nimmt die Übertragung im vom Master bestimmten Modus auf. Soll der Transfer beendet werden, sendet der Master ein Stoppsymbol. Bei der Datenübertragung darf sich das Signal SDA nur ändern, wenn SCL = 0 ist. Im Startsymbol und im Stoppsymbol muß sich SDA ändern während SCL = 1 ist!

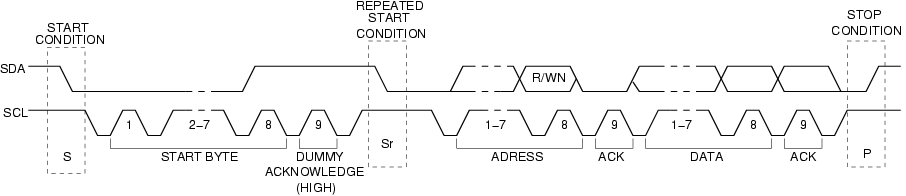

Um einen Slave auch nur durch Software zu realisieren gibt es auch die Möglichkeit ein StartByte zu senden.

Während der Übertragung dürfen sich die Daten nur ändern, wenn der Takt den Null Pegel hat.

Für die Adressierung werden sowohl 7 bit als auch 10 bit-Adressen verwendet, die aber zueinander kompatibel sind. Bei 10 bit-Adressen werden zwei Byte für die Adressierung benutzt, im ersten Byte wird die Bitfolge 11110 als Indikator für ein 10bit-Adresse, die zwei höchstwertigen Bits und ein Bit, das die Richtung des Transfers angibt, übertragen. Im zweiten Byte folgen dann die restlichen acht Adressbits. Neben der genannten Bitfolge 11110 gibt es noch einige weitere für bestimmte Zwecke festgelegte Adressen, die nicht vergeben werden sollten.

| Slaveaddress dezimal | Slaveaddress | R/~W bit | Description |

| 0 | 0000 000 | 0 | General call address (nur write) |

| 0 | 0000 000 | 1 | START byte (immer read) |

| 1 | 0000 001 | X | CBUS address |

| 2 | 0000 010 | X | Address reserved for different bus format |

| 3 | 0000 011 | X | |

| 4-7 | 0000 1XX | X | Reserved for future purposes |

| 124-127 | 1111 1XX | X | |

| 120-123 | 1111 0XX | X | 10 - bit slave addressing (1.Byte mit den oberen beiden Bits) |

Tabelle der reservierten Adressen des I²C Bus.

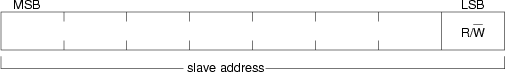

Aufbau der Slave Adresse mit R/~W Flag Slave Adresse 0x12 soll geschrieben werden.

Das Bild zeigt den Aufbau der 7 Bit Adresse oder das 1. Byte einer 10 Bit Adresse (siehe letzte Zeile in obiger Tabelle). Auch hier ist das Richtungsbit im LSB anzugeben. Das Richtungsbit legt die Richtung der Daten zwischen Master und Slave fest. Ist das Bit 1 werden Daten vom Slave zum Master transportiert (read), ist das Bit 0 werden die Daten vom Master zum Slave transportiert (write). Die folgenden Bilder zeigen den Aufbau der beiden Zyklenarten.

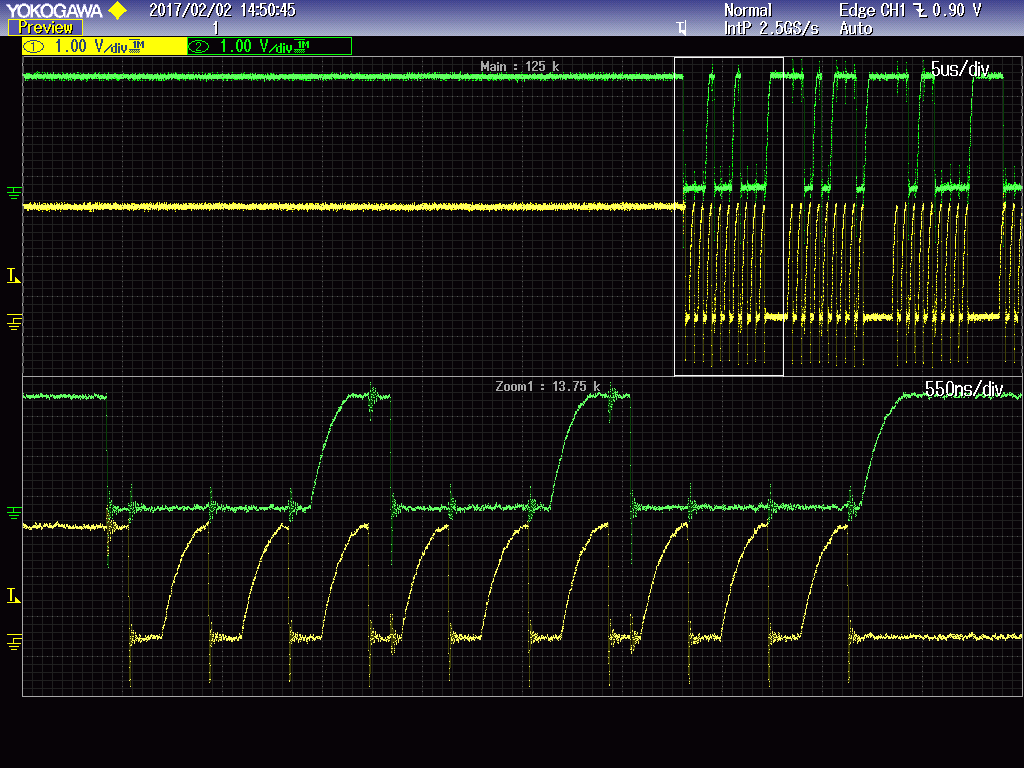

Als Signaldiagramm sieht ein solcher Zyklus wie folgt aus:

Beide Zyklen können auch kombiniert werden. Soll bei einem I²C Slave EEPROM eine Speicherzelle gelesen werden, dann müssen zu erst die Byte der EEPROM Adresse in den Slave geschrieben werden um dann die Datenbyte der Adresse zu lesen. Man lässt dabei am Ende des Schreibzyklus den STOP Befehl weg und beginnt sofort mit einem neuen START das Lesen der Daten. Bei dem erneuten START muss die I²C Adresse noch einmal gesendet werden, bevor man die Daten lesen kann. Erst am Ende beider Zyklen kommt dann der STOP Befehl. Die Anzahl der übertragenen Byte in beiden Zyklen ist dabei vom Typ des EEPROM und damit von der Größe der Adresse und der Breite der Daten abhängig.

Ein solches Signalspiel mit dem senden von 2 Byte gefolgt vom Lesen von 3 Byte ist auch im Protokoll des Datentransfers zwichen einem SpartanMC Master und Slave auf einem ml605 zu sehen. Alle Dateien zum Test können auf der Seite zum I²C Master herunter geladen werden.

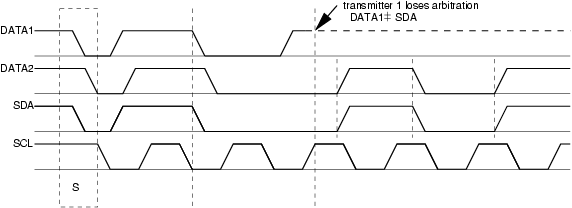

Der I²C Bus ist auch multimasterfähig, daher kann es vorkommen, dass 2 Master zur gleichen Zeit das Senden beginnen. Beim Senden lesen daher die Master ihre eigenen Daten immer zurück. Der Master, der zuerst erkennt das seine Daten nicht auf dem Bus ankommen beendet daraufhin das Senden. Diesen Vorgang Zeigt das folgende Bild.

Dadurch hat das Senden an eine niedrige Adresse immer eine höhere Priorität als das Senden an eine hohe Adresse.

Bei den I²C Slave Modulen gibt es 2 Arten der Behandlung des letzten Daten Byte im Read Mode. Bei manchen Slaves darf der Empfang des letzten Bytes nicht mit ACK bestätigt werden. Für den SpartanMC I²C Master sind daher für die Read Operationen jeweils 2 Funktionen implementiert, die das letzte Byte entweder mit ACK oder mit NAK beantworten. Im Manual des Slave muss nachgelesen werden welche Funktion zur Arbeit mit dem Slave eingesetzt werden muss.

SpartanMC I²C Master

SpartanMC I²C Slave

WEB-Seiten mit Informationen zur Funktion des I²C

http://www.sprut.de/electronic/pic/grund/i2c.htmhttp://de.wikipedia.org/wiki/I2C