Timer Compare

Funktion

Im Compareregister kann ein Vergleichswert zum Timerwert eingestellt werden, bei dessen Erreichen kann wahlweise ein Interrupt ausgelöst und/oder ein Ereignis am Output-Pin des Moduls ausgelöst werden. Der Output-Pin kann gesetzt, zurückgesetzt oder negiert werden.Ist Bit 4 im COMP_CTRL Register gesetzt, dann wird eine 2. Betriebsart aktiviert bei der am Ausgang des Moduls eine Aktion bei Gleichheit des Zählers mit dem COMP_DAT Register und wenn der Zähler gleich Null ist erfolgt. Mit dem Wert im COMP_DAT Register kann dabei die Breite des Impuls am Ausgang bei konstanter Frequenz eingestellt werden.

Register

| Offset | Register | Funktion | Zugriff |

| 0 | COMP_CTRL | Steuerregister | read/write |

| 1 | COMP_DAT | Vergleichswert | read/write |

Das Steuerregister COMP_CTRL enthält alle zur Steuerung der Funktionen des Compare-Moduls nötigen Bits. Bei einem Reset werden alle Bits mit Null initialisiert. Auf das Register kann lesend und schreibend zugegriffen werden.

In dem Register COMP_DAT steht der Vergleichswert, bei dem ein Ereignis ausgelöst wird. Bei einem Reset werden alle Bits mit Null initialisiert. Auf das Register kann lesend und schreibend zugegriffen werden.

Bei jedem Zugriff auf eines der beiden Ports wird das Interruptsignal zurückgesetzt. Ist für das Ausgangssignal der Mode "Ausgang setzen(=1)" eingestellt, dann wird der Ausgang auf 0 gesetzt und ist der Mode "Ausgang zurücksetzen(=0)", dann wird der Ausgang auf 1 gesetzt.

| COMP_CTRL | Funktion | ||

| Bit 0: | Compare enable: 0 = disable, 1 = enable | ||

| Bit 1: | Int enable: 0 = disable, 1 = enable | ||

| Bit 2 bis 4: | 4 3 2 Mode Select bei Bit 4 = 0: | ||

| 0 0 0: Ausgang bleibt gleich | |||

| 0 0 1: Ausgang setzen(=1) | |||

| 0 1 0: Ausgang zurücksetzen(=0) | |||

| 0 1 1: Ausgang negieren | |||

| Bit 4: | Wenn Bit 4 = 1 ist, wird eine Aktion beim Nulldurchgang und bei Gleichheit mit COMP_DAT ausgeführt. Durch Veränderung des Wertes in COMP_DAT kann dann die Breite des Impulses am Ausgang verändert werden. Es ist also eine Impuls breiten Modulation nur durch Verändern des Wertes im COMP_DAT Registeer möglich. | ||

| Bit 2 bis 4: | 4 3 2 Mode Select bei Bit 4 = 1: | ||

| 1 0 0: Ausgang bleibt gleich | |||

| 1 0 1: Ausgang auf 1 setzen bei Gleichheit des Timer mit COMP_DAT — Ausgang auf 0 setzen wenn der Timer = 0 ist. | |||

| 1 1 0: Ausgang auf 0 setzen bei Gleichheit des Timer mit COMP_DAT — Ausgang auf 1 setzen wenn der Timer = 0 ist. | |||

| 1 1 1: Ausgang auf 1 setzen bei Gleichheit des Timer mit COMP_DAT — Ausgang auf 0 setzen wenn der Timer = 0 ist. | |||

| Bit 5: | Output enable: 0 = disable, 1 = enable(nur wenn Ausgang konfiguriert) | ||

| Bit 6: | aktueller Wert des Ausgabebit (nur lesbar). | ||

| Bit 7 bis 17: | nicht benutzt | ||

compare.h

#ifndef __COMPARE_H

#define __COMPARE_H

#define COMPARE_EN (1 << 0) // Compare Enable

#define COMPARE_EN_INT (1 << 1) // Compare Interrupt Enable

#define COMPARE_MODE (1 << 2) // Mode Bit 0

#define COMPARE_NON_FRQ (CMP_MODE * 0) // Ausgang bleibt gleich

#define COMPARE_SET_OUT (CMP_MODE * 1) // Ausgang setzen(=1)

#define COMPARE_CLEAR_OUT (CMP_MODE * 2) // Ausgang zurücksetzen(=0)

#define COMPARE_TOGGLE_OUT (CMP_MODE * 3) // Ausgang negieren

#define COMPARE_NON_IMP (CMP_MODE * 4) // Ausgang bleibt gleich

#define COMPARE_C0_N1 (CMP_MODE * 6) // Ausgang = 0 wenn Timer = CMP_DAT ist -- Ausgang = 1 wenn Timer = 0 ist.

#define COMPARE_C1_N0 (CMP_MODE * 7) // Ausgang = 1 wenn Timer = CMP_DAT ist -- Ausgang = 0 wenn Timer = 0 ist.

#define COMPARE_EN_OUT (1 << 5) // Compare Output Enable

#define COMPARE_VAL_OUT (1 << 6) // Compare Output Value

typedef struct cmp {

volatile unsigned int CMP_CTRL; // (r/w) reset irq

volatile unsigned int CMP_DAT; // (r/w) reset irq

} compare_regs_t;

#endif

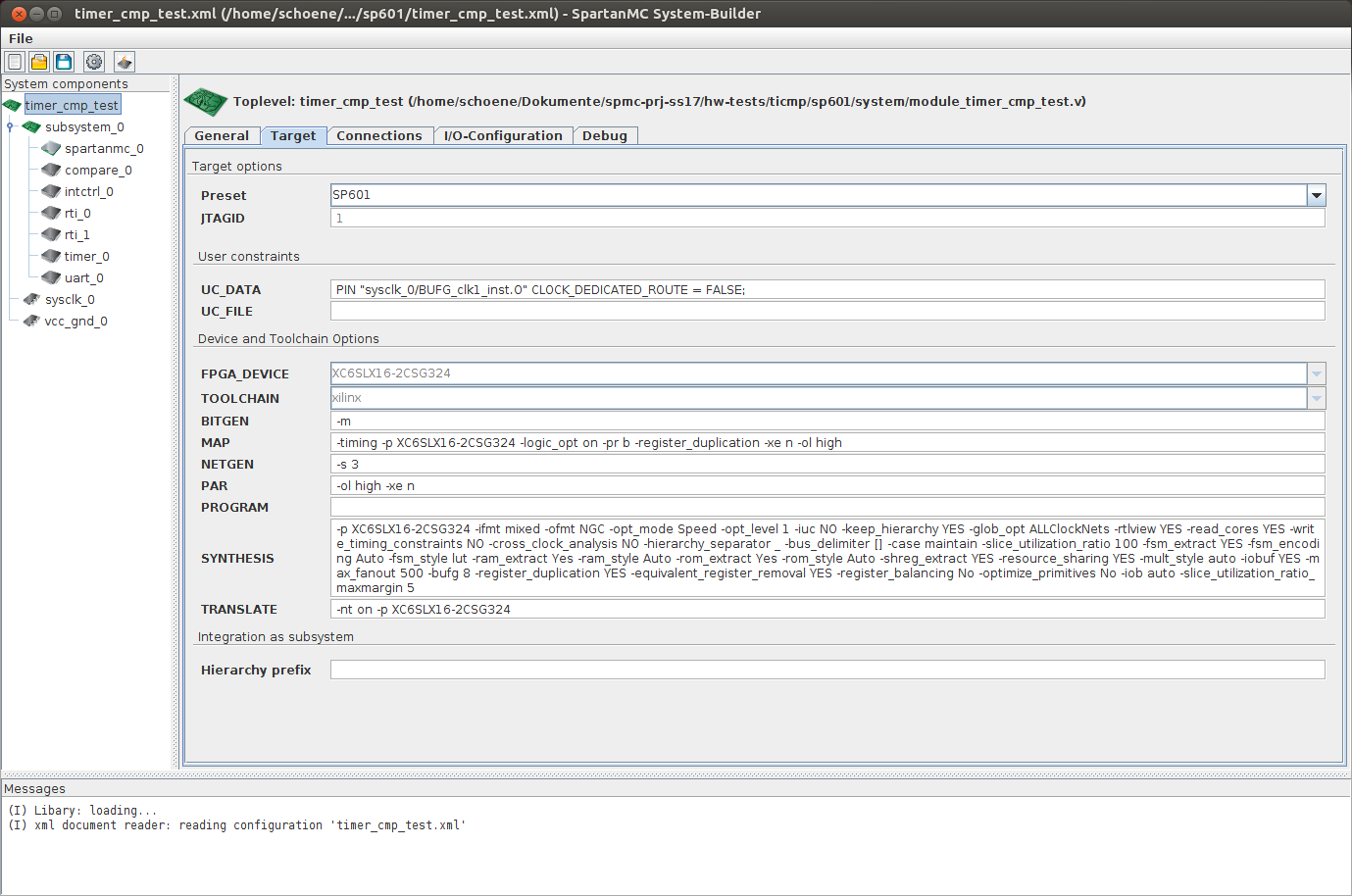

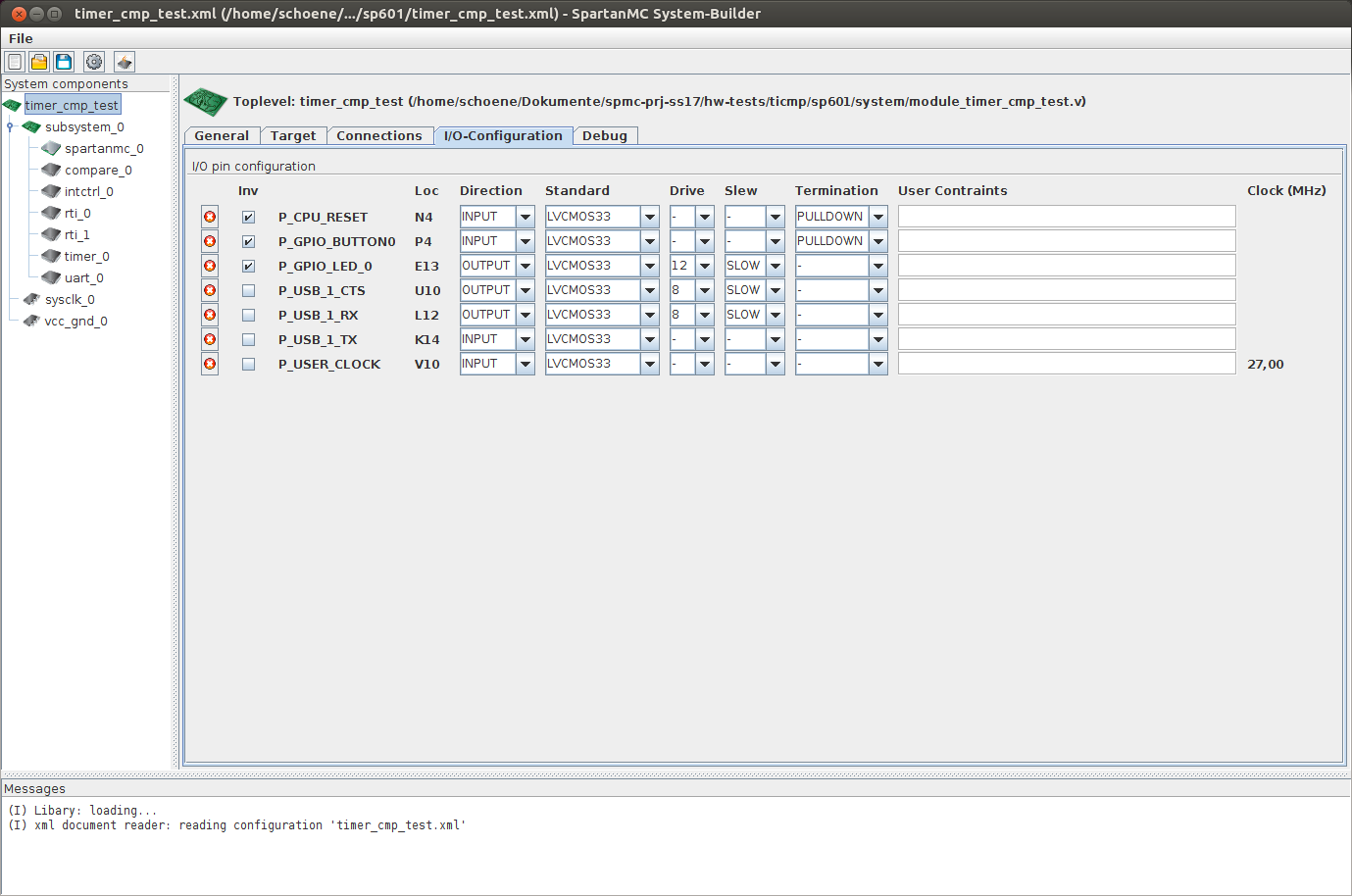

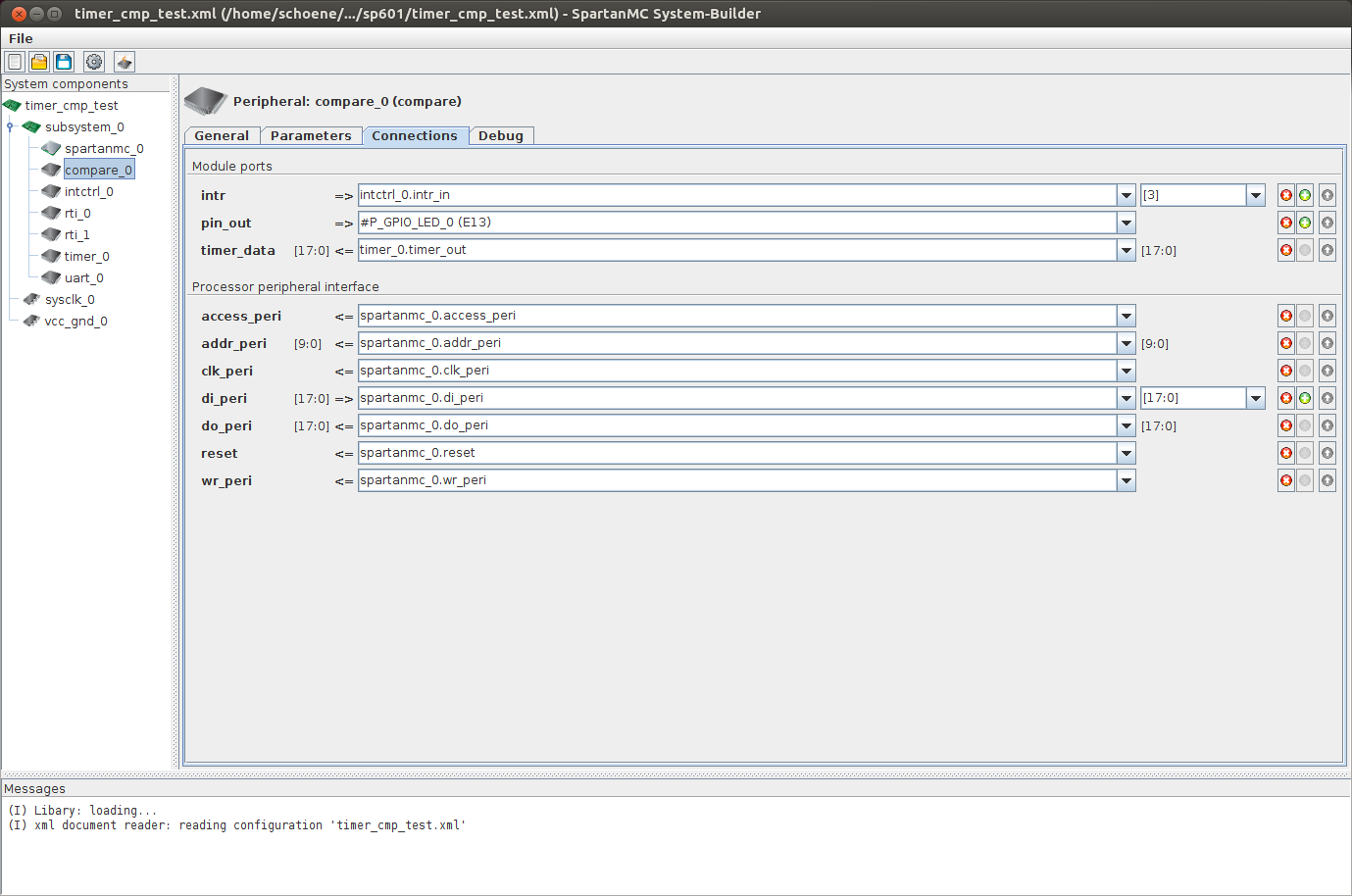

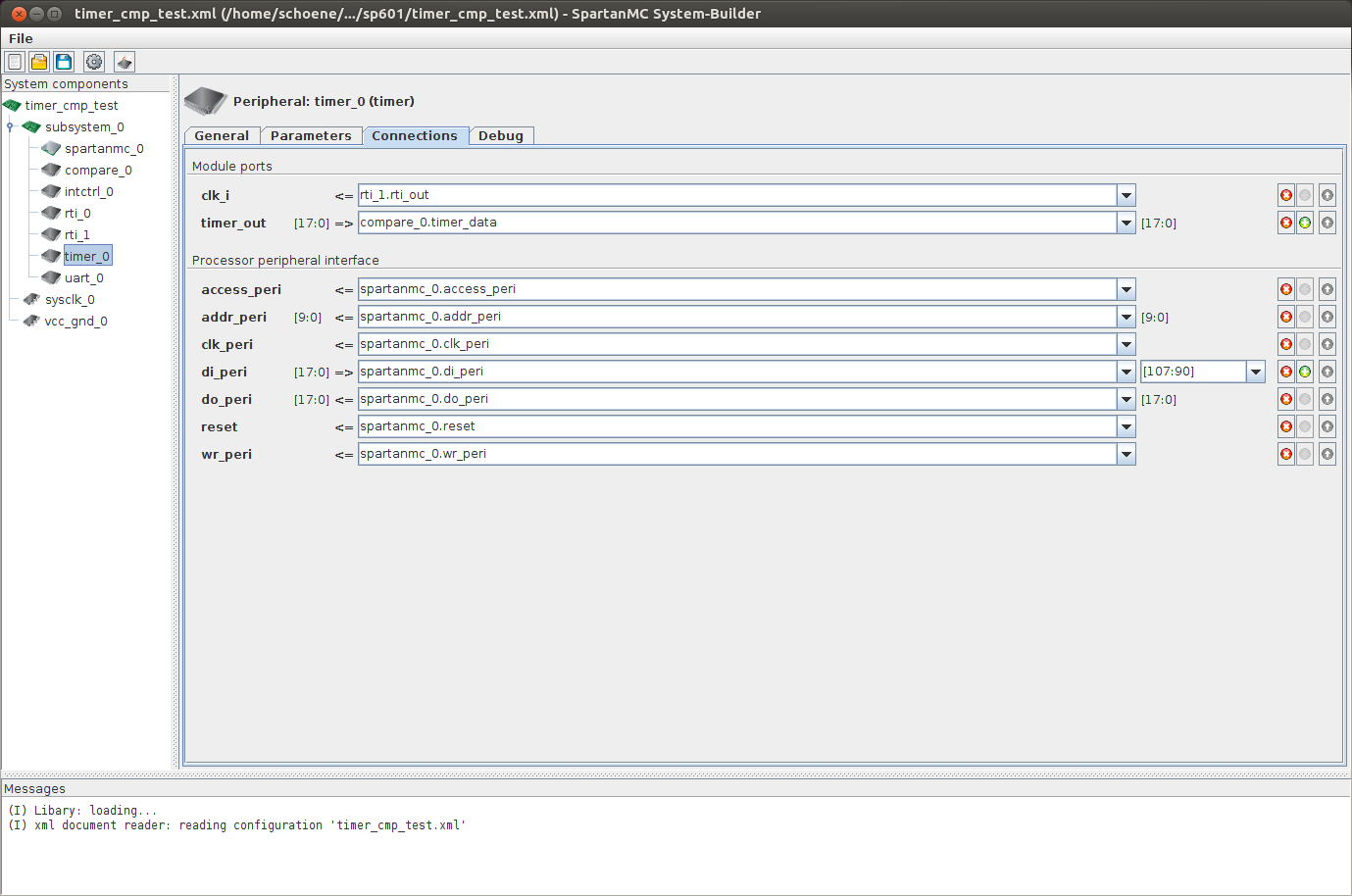

Konfiguration und Instanziierung

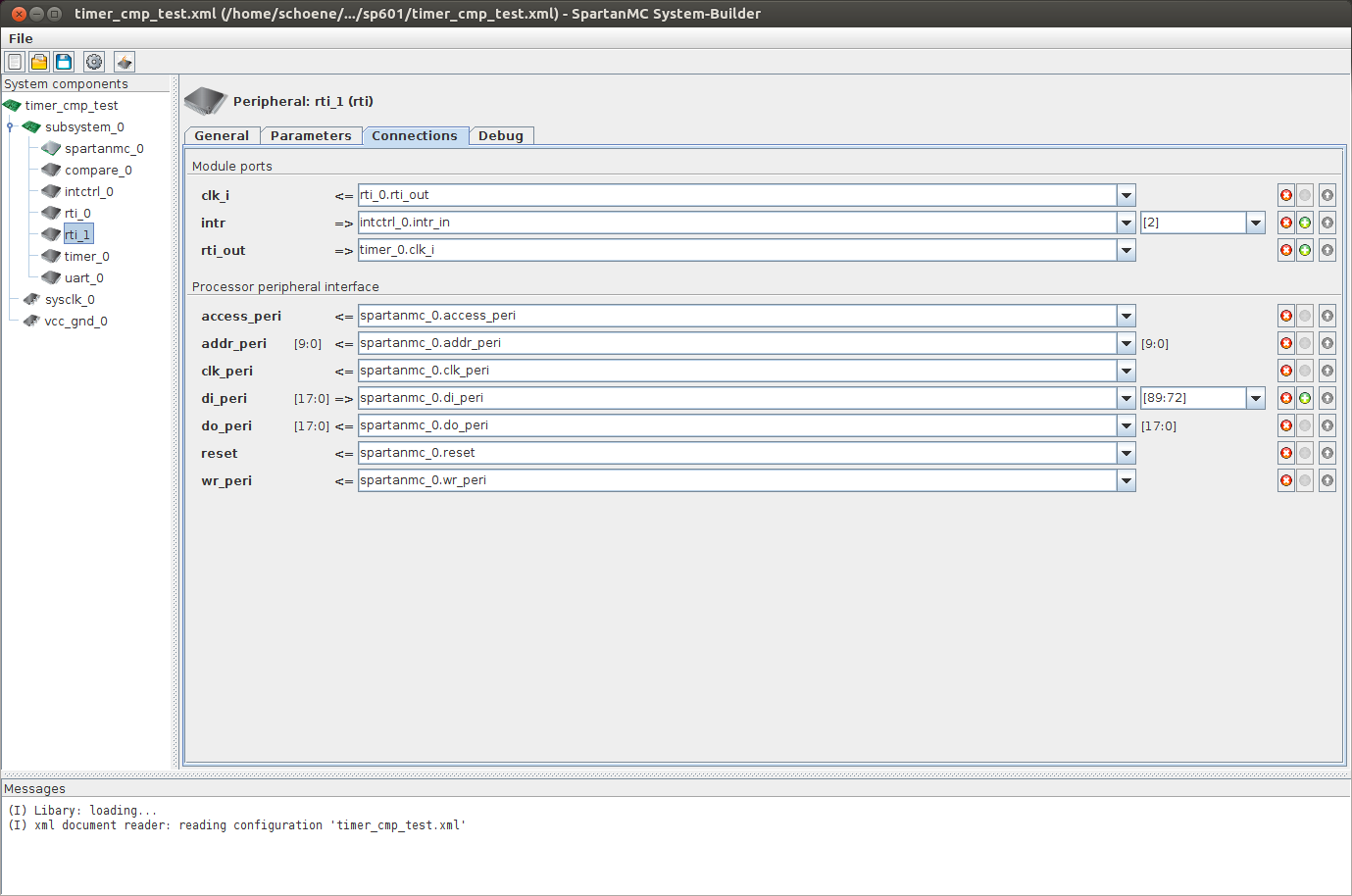

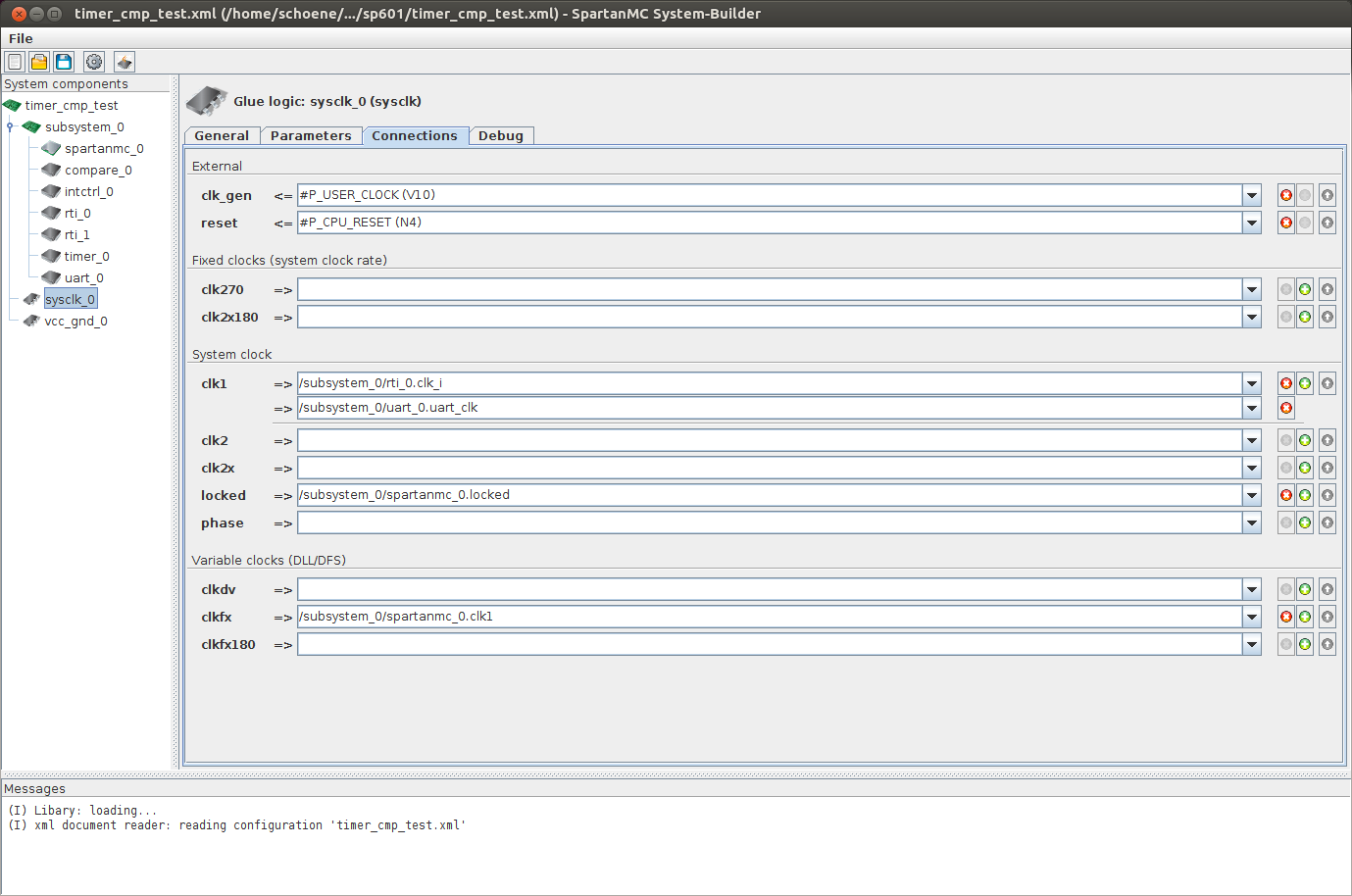

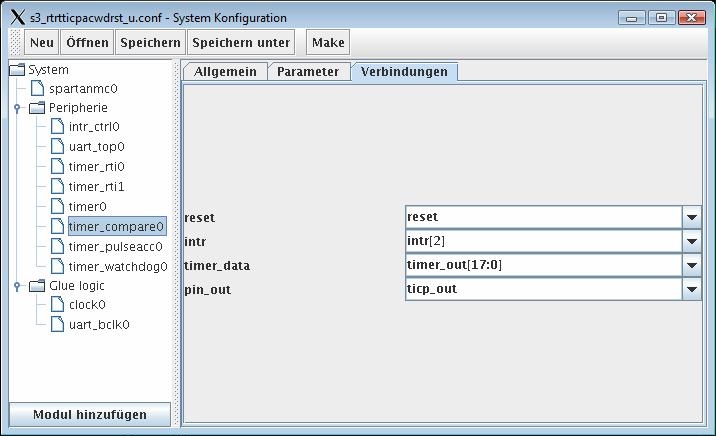

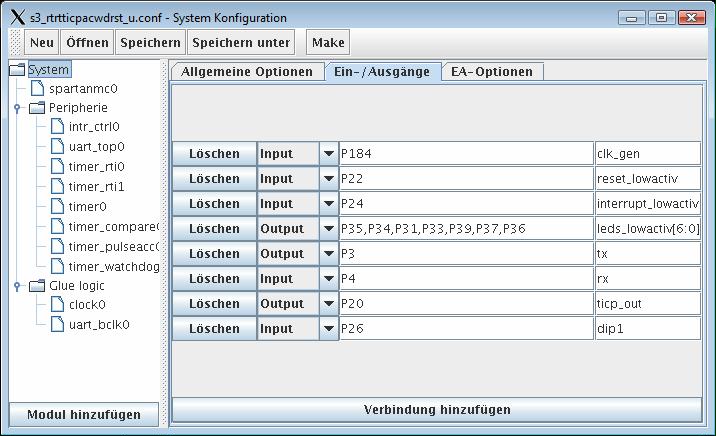

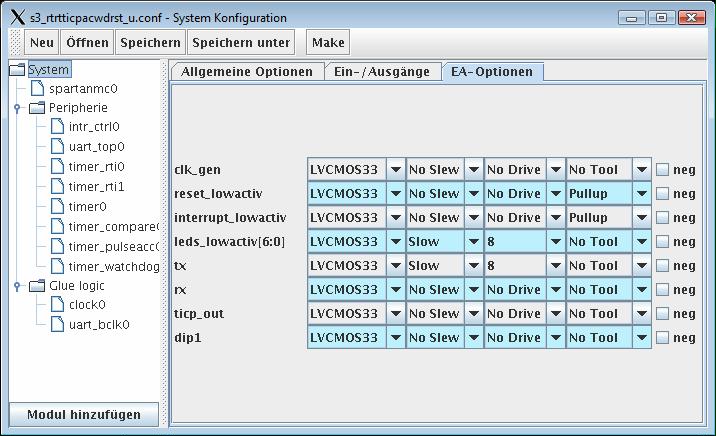

Bei der Instanziierung eines Timer Compare-Moduls wird der Parameter BASE_ADR vom jConfig automatisch eingestellt. BASE_ADR gibt den Offset der Adresse des Moduls zur Basisadresse aller Peripherieregister an. Der Wert besteht aus den oberen sieben Bit der zehn Bit-Adresse eines Moduls (die unteren drei Bit werden nur modulintern benutzt).Die Interruptleitung des Moduls muss an den gewünschten Eingang des Interruptkontrollers angeschlossen werden und der Output-Pin an den Ausgang des Top Level Moduls. Dieser muss dann noch den Pins des FPGA im jConfig zugeordnet werden. Um den Modul zu nutzen muss auch ein TIMER implementiert werden, und dessen 18 Bit Ausgang timer_out[17:0] mit timer_data dieses Moduls verbunden werden.

Testprogramm zur Tonfrequenz Erzeugung und Protokolle.

Programm zum Test der Tonfrequenz Erzeugung als C-Quelle, und Liste. Protokoll des Programms zur Tonfrequenz Erzeugung. Es wird durch betätigen von Taster 1, 2 oder 3 ein Ton mit fester Länge ausgegeben. Die Länge kann durch Eingabe von 1 ... 9 an der Konsole von 2 bis 10 Sekunden variiert werden.Konfigurationen für das Testprogramm zum Download:

- Für das sp601 Board im BIT Format und im MSK Format. Konfigurations Datei für das SP601 Board.

Testprogramm eines Türgong und Protokolle.

Programm eines Türgong als C-Quelle, und Liste. Dokumetation des Programms zum Türgong. Es wird durch betätigen von Taster 1 oder 3 ein Melodie ausgegeben bei Taster 2 wird ein Dreiklang 3 mal ausgegeben.Konfigurationen für das Testprogramm zum Download:

- Für das sp601 Board im BIT Format und im MSK Format. Konfigurations Datei für das SP601 Board.

- Für das 3estk Board im BIT Format und im MSK Format. Konfigurations Datei für das 3estk Board. C-Quelle und Liste Datei. (Taste West = Melodie / Taste Ost = 3 Klang.)

Testprogramm zur Impulsbreitenmodulation und Protokolle.

Programm zum Test der Impulbreiten-Modulation als C-Quelle und Liste. Protokoll des Programms zur Impulbreiten-Modulation. Es wird ein etwa 100 Hz Impuls mit einstellbarer Breite für LED3 auf dem sp601 Board ausgegeben. Mit der Impulsbreite wird die Helligkeit der LED eingestellt.Programm zum Test der Impulbreiten-Modulation als ASS-Quelle, Liste und im SpartanMC SPH Format. Protokoll des Programms zur Impulbreiten-Modulation. Es wird ein etwa 1 Hz Impuls mit einstellbarer Breite für LED1 auf dem Memecboard oder für LED7 auf dem Spartan3e Starter Kit erzeugt.

Konfigurationen für das Testprogramm zum Download:

- Für das sp601 Board im BIT Format und im MSK Format. Konfigurations Datei für das SP601 Board.

- Für das Memecboard im BIT Format und im MSK Format.

- Für den Spartan3e Starter Kit im BIT Format und im MSK Format.

Einstellungen für den Timer-Compare neu

Einstellungen für den Timer-Compare alt

SpartanMC 18 Testmonitor vom 17.10.07 :H Modify (h) :M (daddr) Display 18 Bit :D (start1) [end1] Display 9 Bit :D9 (start1) [end1] Fill 9 Bit :F (start1) (end1) (wert) Move 18 Bit :MO (start1) (end1) (start2) Compare 18 Bit :C (start1) (end1) (start2) Search 18 Bit :SE (start1) (end1) (wert) Goto :G (paddr) Goto DataAddr :GD (daddr) Load *.sph :LS [daddr] :M 34090 34090 00000 / 3d 34092 00000 : 340A0 340A0 00000 / 0d 340A2 00000 : 340B0 340B0 00000 / 1 340B2 00000 / 80 340B4 00000 . 340B4 00074 . 340B4 00004 : 340C0 340C0 00000 / 3d 340C2 00000 / 40 340C4 00000 - 340C2 00040 - 340C0 0007D . 340C0 0003D . 340C0 0003D . 340C0 0007D q :