Timer Capture

Funktion

Das Capture-Register speichert bei einem Ereignis am angeschlossenen Eingangs-Pin den aktuellen Timerwert und kann einen Interrupt auslösen. Bei einem Zugriff auf das Daten- oder Steuerregister wird das Interruptflag automatisch zurückgesetzt. Das Modul kann auf Pegel- oder Flankensensitivität eingestellt werden. Hinweis: Wenn der Betriebsmodus auf Pegel detektieren eingestellt ist, dann wird IMMER ein Interrupt ausgelöst, wenn der entsprechende Pegel am Eingang anliegt, nicht nur nach Signaländerungen.Nach einem abgeschlossenen Capture-Vorgang wird das Enable-Bit im Steuerregister zurückgesetzt. Um einen neuen Capture-Vorgang zu starten, muss dieses Bit wieder auf 1 gesetzt werden.

Register

| Offset | Register | Funktion | Zugriff | ||

| 0 | CAP_CTRL | Steuerregister | read/write | ||

| 1 | CAP_DAT | Messwert | read | ||

Das Steuerregister CAP_CTRL enthält alle zur Steuerung der Funktionen des Capture-Moduls nötigen Bits. Bei einem Reset werden alle Bits mit Null initialisiert. Auf das Register kann lesend und schreibend zugegriffen werden.

Das Datenregister CAP_DAT enthält den gemessenen Wert. Bei einem Reset werden alle Bits mit Null initialisiert. Auf das Register kann nur lesend zugegriffen werden.

| CAP_CTRL | Funktionen | ||||

| Bit 0: | Capture enable: 0 = disable, 1 = enable | ||||

| Bit 1: | Int enable: 0 = disable, 1 = enable | ||||

| Bit 2 bis 4: | Mode select: | ||||

| 000: kein Capture | |||||

| 001: nicht benutzt | |||||

| 010: Capture auf fallende Flanke | |||||

| 011: Capture auf steigende Flanke | |||||

| 100: Capture auf Low-Pegel | |||||

| 101: Capture auf High-Pegel | |||||

| 110: Capture auf beliebige Flanke | |||||

| 111: Capture auf beliebige Flanke | |||||

| Bit 5 bis 17: | nicht benutzt | ||||

capture.h

#ifndef __CAPTURE_H

#define __CAPTURE_H

#define CAPTURE_EN (1 << 0)

#define CAPTURE_EN_INT (1 << 1)

#define CAPTURE_EDGE (1 << 2)

#define CAPTURE_NON (CAP_EDGE * 0)

#define CAPTURE_FALLING_EDGE (CAP_EDGE * 2)

#define CAPTURE_RISING_EDGE (CAP_EDGE * 3)

#define CAPTURE_LOW_LEVEL (CAP_EDGE * 4)

#define CAPTURE_HIGH_LEVEL (CAP_EDGE * 5)

#define CAPTURE_ANYTHING_EDGE (CAP_EDGE * 7)

typedef struct cap {

volatile unsigned int CAP_CTRL; // (r/w) reset IRQ

volatile unsigned int CAP_DAT; // (r) reset IRQ

} capture_regs_t;

#endifKonfiguration und Instanziierung

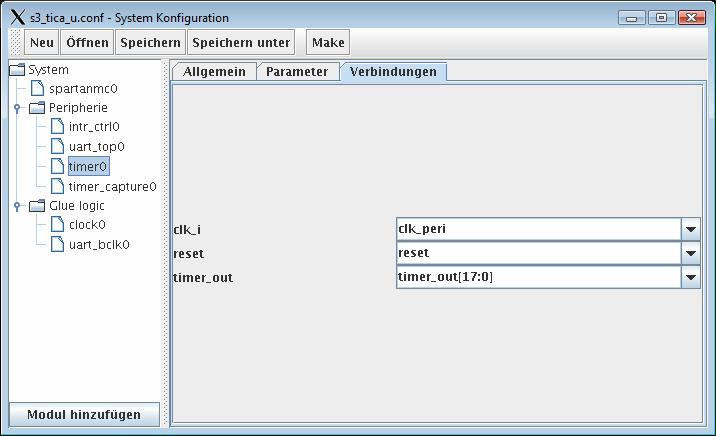

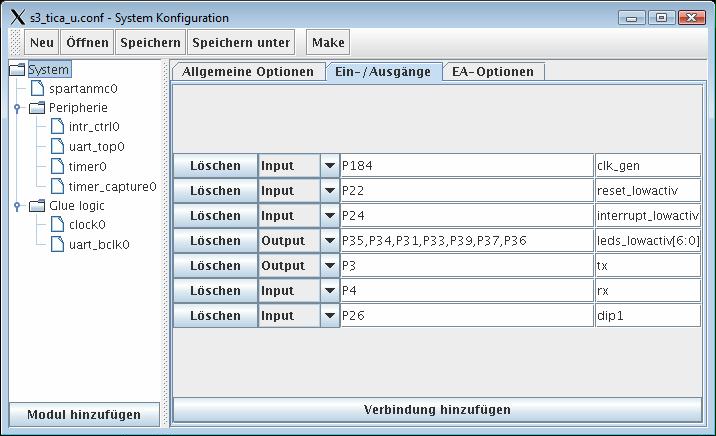

Bei der Instanziierung eines Timer Capture-Moduls wird der Parameter BASE_ADR vom jConfig automatisch eingestellt. BASE_ADR gibt den Offset der Adresse des Moduls zur Basisadresse aller Peripherieregister an. Der Wert besteht aus den oberen sieben Bit der zehn Bit-Adresse eines Moduls (die unteren drei Bit werden nur modulintern benutzt).Die Interruptleitung des Moduls muss an den gewünschten Eingang des Interruptkontrollers angeschlossen werden und der Input-Pin an den Eingang des Top Level Moduls. Dieser muss dann noch den Pins des FPGA im jConfig zugeordnet werden. Um den Modul zu nutzen muss auch ein TIMER implementiert werden, und dessen 18 Bit Ausgang "timer_out 17:0" mit timer_data dieses Moduls verbunden werden.

Einstellungen für den Timer Capture

Der Capture Modul muss immer mit einem Timer Modul konfiguriert werden. Im Timer läuft dann der Zähler, dessen Wert beim erreichen des Ereignis am Eingang des Capture Moduls in diesem gespeichert wird und vom Programm abgefragt werden kann. Dazu wird das 18 Bit breite Signal "timer_out 17:0" zwischen beiden Modulen verbunden. Der Eingang des Capture Modul wurde mit dem Schalter DIP1 des Board verbunden.

Überprüfung der Funktion mit Kommandos des Monitors

Aktivierung des Timer auf der Adresse 0x340A0SpartanMC 18 Testmonitor vom 17.10.07 :H Modify (h) :M (daddr) Display 18 Bit :D (start1) [end1] Display 9 Bit :D9 (start1) [end1] Fill 9 Bit :F (start1) (end1) (wert) Move 18 Bit :MO (start1) (end1) (start2) Compare 18 Bit :C (start1) (end1) (start2) Search 18 Bit :SE (start1) (end1) (wert) Goto :G (paddr) Goto DataAddr :GD (daddr) Load *.sph :LS [daddr] :M 340A0 340A0 00000 340A2 00000 / 3ffff 340A4 00000 - 340A2 3FFFF - 340A0 00000 / 1f 340A2 3FFFF 340A4 15A03 . 340A4 063EA . 340A4 1FBBF . 340A4 3800E q :

Der Wert 0x3FFFF stellt den maximalen Wert für den Zähler an der Leitung "timer_out 17:0" dar. Mit der 0x1F wird der Timer mit maximalem Vorteiler aktiviert. Danach sieht man, wie sich der Zähler auf der Adresse 0x340A4 ständig verändert.

Aktivierung des Capture auf der Adresse 0x340B0

Nun kann der Capture Modul aktiviert und getestet werden. Mit einer 0xD auf das Steuerregister wird der Modul für eine steigende Flanke am Eingang aktiviert. Wird nun mit DIP1 diese Flanke erzeugt, dann wird der aktuelle Wert des Zählers in das Datenregister des Capture Moduls auf Adresse 0x340B2 gespeichert. Danach ist der Modul wieder deaktiviert. Nach einer erneuten Aktivierung wird dann der alte Zählerwert mit einem neuen Wert überschrieben, wenn man mit DIP1 wieder eine steigende Flanke erzeugt.

:M 340B0 340B0 00000 / d 340B2 00000 . 340B2 15D96 . 340B2 15D96 . 340B2 15D96 . 340B2 15D96 - 340B0 0000C / d 340B2 15D96 . 340B2 15D96 . 340B2 15D96 . 340B2 162E2 . 340B2 162E2 . 340B2 162E2 . 340B2 162E2 . 340B2 162E2 . 340B2 162E2 - 340B0 0000C /wert - + . :adr Q 340B0 0000C / d 340B2 162E2 . 340B2 162E2 . 340B2 162E2 . 340B2 0975A . 340B2 0975A q :