Timer Basismodul

Funktion

Der Timer beinhaltet einen von 2 bis 256 in 8 Stufen konfigurierbaren Vorteiler, der auch ausgeschalten werden kann. Der Takteingang dieses Vorteilers kann beliebig mit dem Systemtakt, einem DCM Ausgang oder dem Ausgang eines zweiten Timers verbunden werden. Der Ausgang des Vorteilers treibt den Takt eines 18bit-Zählers, der bis zu einem programmiebaren Wert hochzählt und dann wieder neu startet. Zusammen mit diesem Modul können RTI-, Watchdog-, Capture-, Compare- und Pulse Accumulator-Module in beliebiger Anzahl generiert werden.Register

| Offset | Register | Funktion | Zugriff |

| 0 | TIMER_CTRL | Steuerregister | read/write |

| 1 | TIMER_DAT | max. Timerwert | read/write |

| 2 | TIMER_VALUE | aktueller Timerwert | read/write |

Das Steuerregister TIMER_CTRL enthält alle zur Steuerung der Funktionen des Timer-Zählers nötigen Bits. Bei einem Reset werden alle Bits mit Null initialisiert. Auf das Register kann lesend und schreibend zugegriffen werden.

Das Datenregister TIMER_VALUE gibt den aktuellen Zählerstand an. Bei einem Reset werden alle Bits mit Null initialisiert. Auf das Register kann lesend und schreibend zugegriffen werden.

Das Datenregister TIMER_DAT speichert den Wert, bis zu dem der Timer zählen soll. Bei einem Reset werden alle Bits mit Null initialisiert. Auf das Register kann lesend und schreibend zugegriffen werden.

| TIMER_CTRL | Funktionen | ||

| Bit 0: | Timer enable: 0 = disable, 1 = enable | ||

| Bit 1: | Teiler enable: 0 = disable, 1 = enable | ||

| Bit 2 bis 4: | Vorteiler: | ||

| 000: 2¹ | |||

| 001: 2² | |||

| 010: 2³ | |||

| 011: 2⁴ | |||

| 100: 2⁵ | |||

| 101: 2⁶ | |||

| 110: 2⁷ | |||

| 111: 2⁸ | |||

| Bit 5 bis 17: | nicht benutzt | ||

timer.h

#ifndef __TIMER_H

#define __TIMER_H

#define TIMER_EN (1<<0)

#define TIMER_PRE_EN (1<<1)

#define TIMER_PRE_VAL (1<<2) // *0 fuer 2^1 bis *7 fuer 2^8

#define TIMER_PRE_2 (TIMER_PRE_VAL * 0)

#define TIMER_PRE_4 (TIMER_PRE_VAL * 1)

#define TIMER_PRE_8 (TIMER_PRE_VAL * 2)

#define TIMER_PRE_16 (TIMER_PRE_VAL * 3)

#define TIMER_PRE_32 (TIMER_PRE_VAL * 4)

#define TIMER_PRE_64 (TIMER_PRE_VAL * 5)

#define TIMER_PRE_128 (TIMER_PRE_VAL * 6)

#define TIMER_PRE_256 (TIMER_PRE_VAL * 7)

typedef struct timer {

volatile unsigned int control; // (r/w)

volatile unsigned int limit; // (r/w)

volatile unsigned int value; // (r/w)

} timer_regs_t;

#endifKonfiguration und Instanziierung

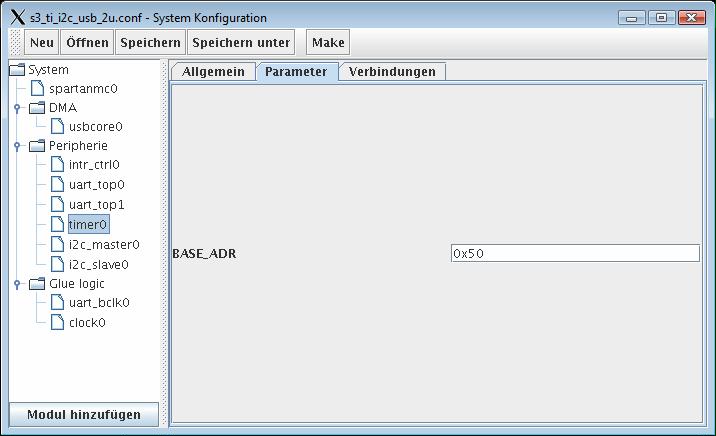

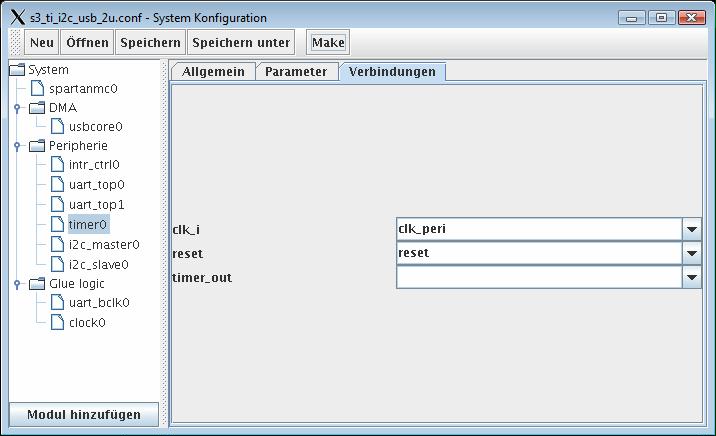

Bei der Instanziierung eines Timer-Moduls wird der Parameter BASE_ADR vom jConfig automatisch eingestellt. BASE_ADR gibt den Offset der Adresse des Moduls zur Basisadresse aller Peripherieregister an. Der Wert besteht aus den oberen sieben Bit der zehn Bit-Adresse eines Moduls (die unteren drei Bit werden nur modulintern benutzt).Das Timer-Modul besitzt einen Ausgang für den Timerwert, für diesen muss ein 18 Bit breiter Bus angelegt werden. Der Modul kann mehrfach angelegt werden, um mit unterschiedlichen Teiler Werten arbeiten zu können dabei kann der 2. Timer auch als clk_i ein Bit von timer_out des 1. Timers nutzen und somit sehr kleine Frequenzen realisieren.

Einstellungen für den Timer

Der Eingang "clk_i" ist der Takt für den Vorteiler des Moduls. Bei Verwendung eines zweiten Timermoduls kann der Eingang auch mit einem Bit des Ausgangs "timer_out 17:0" oder mit dem Ausgang eines RTI Modul verbunden werden. Durch die Kaskadierung von Timer und RTI Modulen sind auch sehr kleine Frequenzen realisierbar.