Umstellung auf neue Pipeline

SpartanMC Core mit 2 Port Registerfile

In dieser Konfiguration wird am Registerfile ein Phasensplitting durchgeführt, um in jedem Takt 2 Register zu lesen und ein Register zu schreiben. Dazu werden alle 4 Taksignale clk1, clk2, clk2x und phase benötigt. Die Variante ist dadurch langsamer als die folgende Variante mit dem 3 Port Registerfile. Die 2 Port Variante benötigt aber einen Blockram weniger.

SpartanMC Core mit 3 Port Registerfile

In dieser Konfiguration arbeiten alle Funktionseinheiten des SpartanMC nur noch mit der positiven Flanke des Taktsignals CLK1. Bei dieser Konfiguration kann CLK1 vom SpartanMC mit CLKFX eines DCM-Moduls verbunden werden. CLK2, CLK2X und PHASE des SpartanMC können unbeschaltet bleiben.

In dieser Implementierung des SpartanMC mit 3 Port Register File stehen jetzt drei Signale zur Verfügung, mit denen der Systemtakt angehalten oder auf eine niedrigere Frequenz zur Laufzeit umgeschaltet werden kann. Damit ist es jetzt möglich die CPU anzuhalten, während eine spezielle IO-Komponente Daten im Speicher erzeugt. Es kann aber auch zur Laufzeit auf eine niedrigere Taktfrequenz umgeschaltet werden, um langsame Funktionseinheiten direkt ansprechen zu können. Die drei neuen Signale sind:

- step_en_off Durch einen High-Impuls wird in den normalen Betriebsmode umgeschaltet.

- step_en_on Durch einen High-Impuls wird in den STEP-Mode umgeschaltet.

- step Mit jeder low-high Flanke an diesem Eingang wird ein Takt für den SpartanMC freigegeben.

Mit einem Schalter kann im jConfig eine der beiden Varianten für den SpartanMC Core ausgewält werden. Achtung, die Beschaltung der Taktsignale wird nicht überwacht!

Aktuelle informationen zur Implementierung

- Geräte für new_pipe

- Konfigurationen aus dem SVN die auf new_pipe umgestellt sind

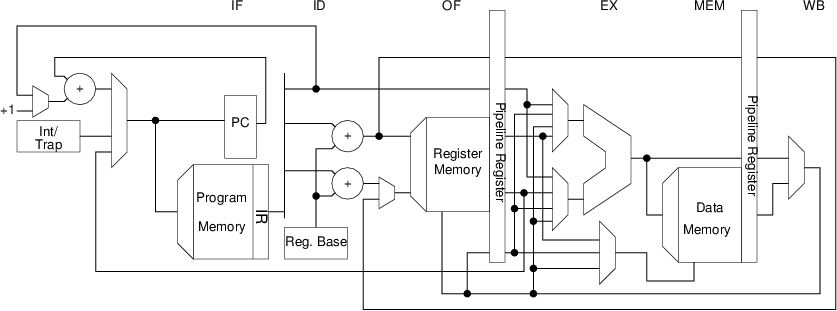

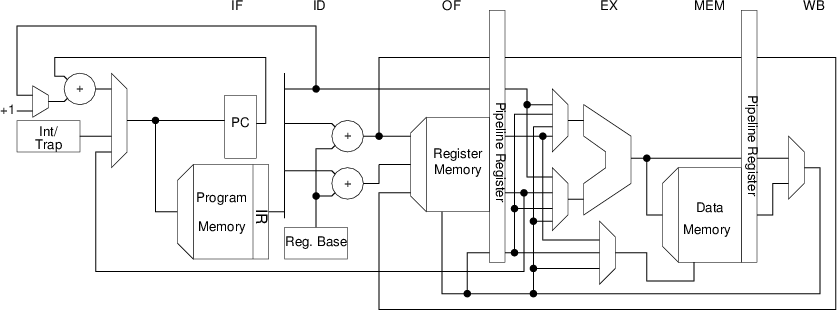

- Pipeline des neuen SpartanMC

- Dekodierung der IO-Adressen für die neue Pipeline